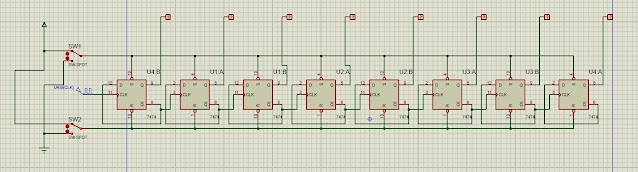

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunkan D flip flop dan

output 8 bit

2. Gambar Rangkaian Simulasi

[Kembali]

3. Vidio SImulasi [Kembali]

4. Prinsip Kerja Rangkaian

[Kembali]

Rangkaian pada percobaan ini adalah up counter dengan menggunakan D Flip-flop. Rangkaian tersebut dibuat sedemikian rupa, agar terjadi kondisi toggle, agar logika nya dapat bertukar-tukar. Apabila input D dihubungkan ke power, maka kondisi logikanya tidak akan berubah-ubah.

Rangkaian di atas merupakan Asyncronus Counter, hal ini dikarenakan clock yang tidak di pakai bersamaan pada setiap flip-flop nya, namun menunggu output dari flip-flop sebelumnya. DIkarenakan memakai Asyncronus counter, maka output dari setiap flip-flop nya tidak akan serempak, namun akan keluar secara bertahap.

Rangakain ini rangkaian Fall time, artinya nilai logika nya akan bertukar saat clock memasuki kondisi fall-time. Flip flop 1 akan mengikuti fall time dari clock, flip-flop 2 mengikuti fall time dari flip-flop 1, dan begitu seterusnya sampai ke flip-flop 8. Kondisi inilah yang menyebabkan terjadi nya counter, karena adanya delay antara satu flip-flop ke flip-flop lainya.

5. Link Download

[Kembali]

Tidak ada komentar:

Posting Komentar